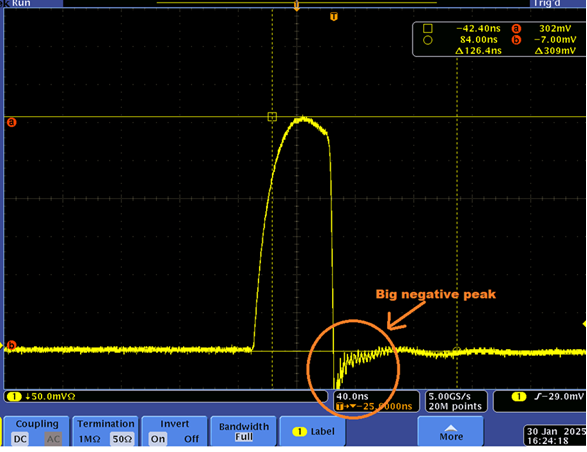

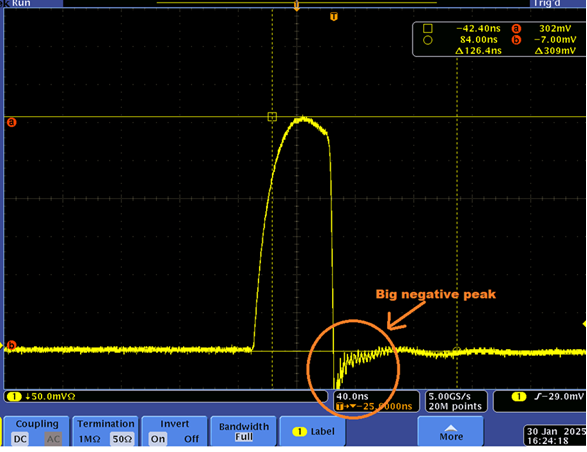

Hello, what are the different effective techniques to reduce the negative peak discharge pulse generated at the EPC GaN FET? it’s quite narrow and sometimes could achieve the level of the discharge pulse. A measurement image is attached.

Hello, what are the different effective techniques to reduce the negative peak discharge pulse generated at the EPC GaN FET? it’s quite narrow and sometimes could achieve the level of the discharge pulse. A measurement image is attached.

Hello,

the waveform depends on details of your circuit and working voltages.

Some missing waveform of capacitor voltage and FET drain voltage will also help to understand. It is better if we can take the discussion offline since you’ll need to share details of your implementation.

Regards